53 Gbps Native GF(2 Composite-Field AES-Encrypt/Decrypt Accelerator for Content-Protection in 45 nm High-Performance Microproces

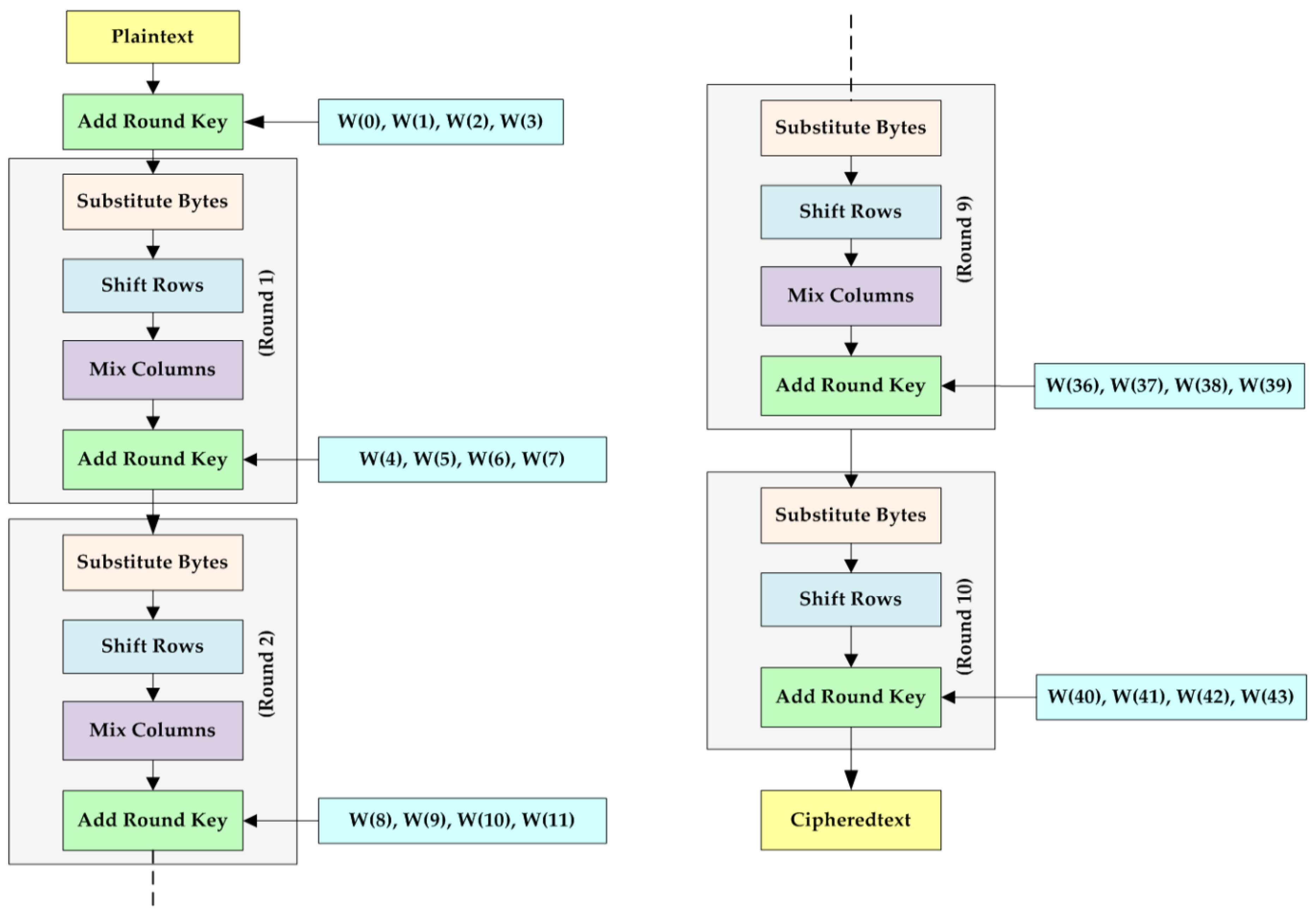

Electronics | Free Full-Text | 10 Clock-Periods Pipelined Implementation of AES-128 Encryption-Decryption Algorithm up to 28 Gbit/s Real Throughput by Xilinx Zynq UltraScale+ MPSoC ZCU102 Platform | HTML

Electronics | Free Full-Text | 10 Clock-Periods Pipelined Implementation of AES-128 Encryption-Decryption Algorithm up to 28 Gbit/s Real Throughput by Xilinx Zynq UltraScale+ MPSoC ZCU102 Platform | HTML

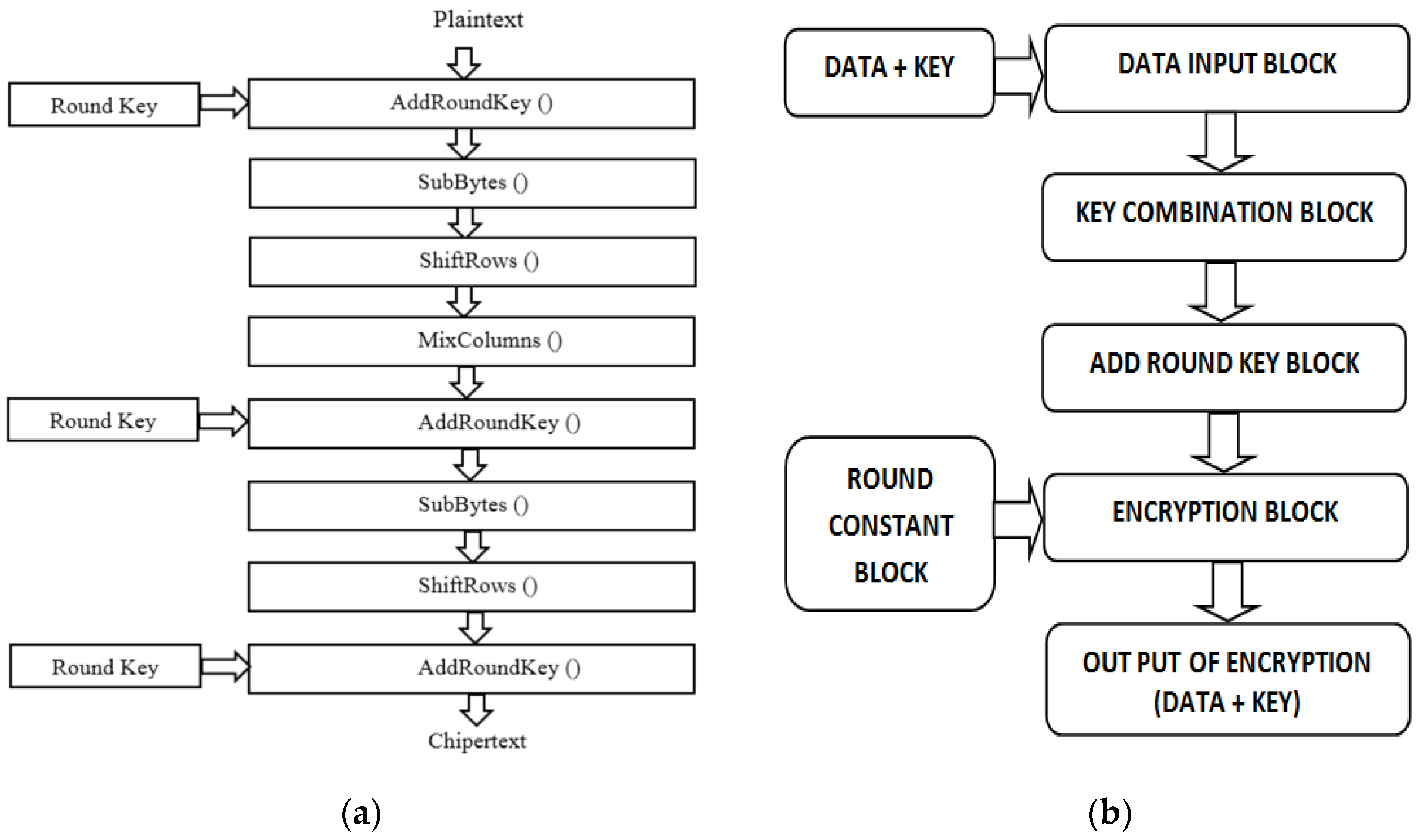

An Introduction to the Advanced Encryption Standard (AES) | by Adrienne Domingus | The Startup | Medium

PDF) Security enhancement of Advanced Encryption Standard (AES) using time-based dynamic key generation